# 集積量子デバイス領域

### 大阪大学大学院工学研究科 電気電子情報工学専攻 教授

## 森 伸 也

#### 1. はじめに

本研究室は、2015年4月1日に発足しました。新しい半導体材料、新しいデバイス構造、新しい動作原理を用いたデバイス・集積システムの実現に向けて、計算物理をベースとした理論的な研究を行なっています。量子デバイスにおいて原子レベルで発現する物理現象の解明から、集積システムの高性能化に至る、幅広い階層をまたぐ研究を行なっています。現在は、松岡俊匡准教授、鎌倉良成准教授と私の3名で研究室を運営しています。

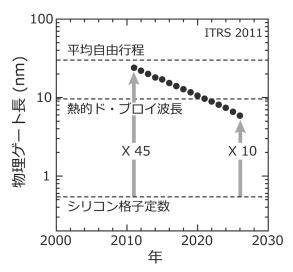

極限まで半導体電子デバイスの微細化が追求され、 量産化されているシリコン MOS 型トランジスタの チャネル長は既に 30 nm を切っています (図 1)。研 究レベルではチャネル長 10 nm 以下のデバイスの動 作も多数報告されています。MOS 型トランジスタで は、サイズの縮小がデバイスの高性能化につながると いう、いわゆるスケーリング則が成り立つため、高性 能化を目指した微細化が行われてきました。しかし、 デバイスが極度に微細化された結果、従来の単純なス ケーリング則のみによる性能向上の限界が顕在化して

図 1: シリコン MOS 型トランジスタのゲート長の推移と将来 予測(国際半導体技術ロードマップより引用)。比較の ため、シリコンにおける特徴的な長さもプロットした。 ゲート長は、すでに、低電界における電子の平均自由行 程より短くなっており、室温における熱的なド・ブロイ 波長に近づいている。

きました。現在、この状況の打破を目指して、様々な デバイス構造・半導体材料・システムが提案され、試 作されています。

デバイス構造・材料レベルにおいては、ナノワイヤ 構造などの立体構造デバイスの導入や、カーボン系材 料やファンデルワールス型2次元物質などの新規材料 の導入が検討されています。一方、システムレベルに おいては、これまでのフォンノイマン型アーキテク チャ内における高集積化・高速化に関する研究開発に 加え、生体情報処理機構を模した技術の応用や、量子 情報処理デバイス・量子コンピュータなどが検討され ています。さらに、デバイスが極度に微細化された結 果として、増大し続けている情報処理に伴うエネル ギー消費を抑えるため、トンネルトランジスタなどの 新しい原理に基づくデバイスを用いた低消費電力シス テムの開発や、システムレベルにおける熱マネージメ ント技術開発なども重要な課題となっています。

以上で述べたような、新材料・新構造・新原理を用 いたデバイス・集積システムの実現のためには、原子 レベルで発現する物理現象の解明から、集積回路・シ ステムレベルにおける性能評価に至る、非常に幅広い 階層をまたぐ研究が必須です。回路システム構成に応 じたデバイスの開発、ならびに、個々のデバイスの特 徴を生かした回路システムの開発が重要です。1990 年代はじめに、大型計算機において、集積回路を構成 するトランジスタが、バイポーラ型から CMOS 型へ と変更されました。デバイスの集積度やモジュールの 発熱などの観点から、システム全体で総合的に判断し た場合、CMOS型トランジスタの方が勝るようにな り、変更されました。このように、回路システム構成 に応じたデバイスの選択が、高性能なシステムの開発 において重要です。一方、抵抗変化型メモリを、脳の シナプスを模した回路に応用することにより、画像処 理などにおいて高い性能が実現される、というような、 個々のデバイスの特徴を生かした回路・システムの開 発も重要です。

以上のような背景のもと、本研究室は、量子デバイスを集積したシステムの高集積化・高機能化・低消費電力化を目指し、計算機を利用した理論的な手法により、次世代量子デバイス・システムの実現に向けた課題に取り組んでいます。ただ、研究室が発足してから1ヶ月あまりということですので、以下では、2015年3月末まで行なってきましたJST・CRESTプロジェクト「原子論から始まる統合シミュレータの開発」(研究代表者:森伸也)の内容を紹介させて頂きます。

#### 原子論から始まる統合シミュレータの開発

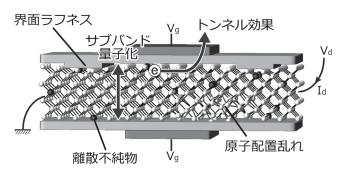

半導体デバイスのシミュレーションは、これまでは、 ドリフト・拡散モデルなど、電子の運動を古典力学で 扱うという枠組みの中で行われてきました。しかし、 ゲート長が10 nm 以下の極めて微細なデバイスにお いては、電子が量子力学に従って運動するという量子 性や、デバイスが原子から構成されているという原子 論的な効果が重要な役割を演じます(図2)。極微細 デバイスにおける電子の流れをゲート電極で制御する 様相を、水の流れを水門で制御するというような古典 的な描像で捕らえることはできません。従来とは本質 的に異なるコンセプトでデバイス設計を行わなければ なりません。そこで、原子スケールのデバイスで顕在 化する物理現象を量子論に基づいて取り扱うことによ り、次世代デバイスの性能予測機能を有する統合シ ミュレータの実現を目指した研究を行なってきまし た。統合シミュレータの核となる、原子論に基づく量 子輸送シミュレータは、膨大な計算時間を必要とする ため、新しい計算アルゴリズムの導入により短時間処

図 2:微細デバイスにおいて顕在化する量子論的・原子論的効果の模式図。代表的な量子論的効果には、極めて狭い空間に電子が閉じ込められエネルギー準位が離散的となるサブバンド量子化や、薄いゲート絶縁膜を電子がトンネル効果によりリークするゲートトンネルなどがある。原子論的な効果には、デバイスをもはや連続体と見なせないという効果の他に、界面ラフネス散乱や離散不純物効果などがある。

理を可能とすることを目指した研究を行なってきました。

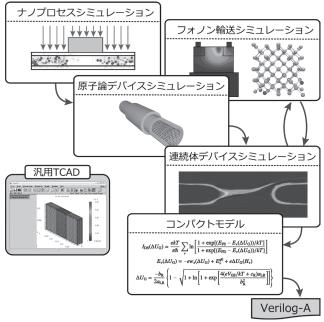

図3に、開発した統合シミュレータの概念図を示します。統合シミュレータは、①ナノプロセスシミュレーション(慶應義塾大学・伊藤公平、植松真司)、②原子論デバイスシミュレーション(大阪大学・森伸也、鎌倉良成)、③連続体デバイスシミュレーション(神戸大学・土屋英昭)、④フォノン輸送シミュレーション(大阪大学・鎌倉良成、立命館大学・宇野重康)、⑤コンパクトモデル(立命館大学・宇野重康)のブロックから成り(括弧内はCRESTチーム内の役割分担)、各階層間を物理パラメータで接続しています。また、一般のユーザーが簡便に利用できるよう、汎用TCADシステムと量子輸送シミュレータとの連携も図っています。

図3:原子論から始まる統合シミュレータの概念図

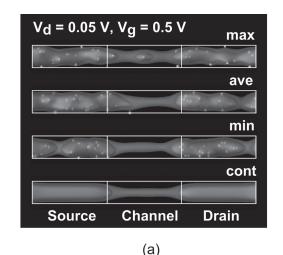

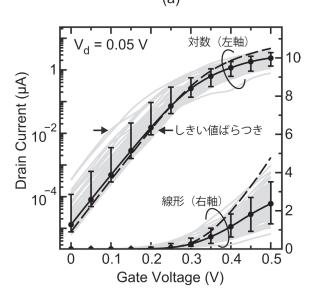

ナノプロセスシミュレーションでは、不純物の挙動を予測するために最適なモンテカルロシミュレーションを実現しました。シリコンバルクの実験結果や慶應義塾大学・伊藤公平グループが構築した厳密モデル(Uematsuモデル)に基づく計算結果と比較して、パラメータの精度向上を図っています。シリコンナノワイヤにイオン注入したヒ素やボロンのアニール後の分布を調べることができます。得られた分布を、量子輸送シミュレータに導入し、離散不純物配置がナノワイヤトランジスタの電気的特性に及ぼす影響を調べることができます(図4)。

図 4:離散不純物配置がナノワイヤトランジスタの電気的特性に及ぼす影響。ゲート長 10 nm、3 nm × 3 nm 正方形断面シリコンナノワイヤトランジスタの離散不純物分布を動的モンテカルロ法により計算し、非平衡グリーン関数法に基づくデバイスシミュレータにより電流電圧特性を計算した結果。(a) 不純物配置(点) と等電子密度面。上から、最大、平均、最低電流デバイスの場合。ゲートマスクがあるにも関わらず、チャネル領域に数個の不純物が拡散侵入している様子が分かる。一番下は、従来の連続ドープモデルに基づく結果。(b) 伝達特性。灰色の線は不純物配置が異なる 100 個のサンプルの結果、黒点は中央値、エラーバーは 5% 点から 95% 点を表す。破線は、連続ドープの場合。数個の侵入不純物が大きなしきい値ばらつきを引き起こす。

(b)

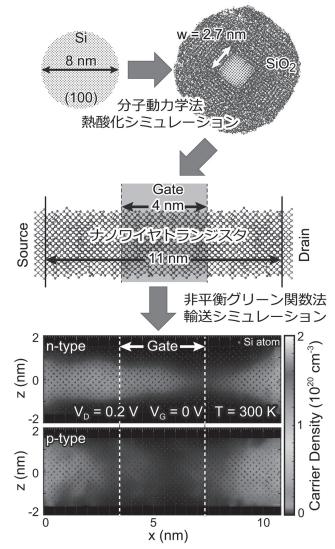

原子論デバイスシミュレーションは、我々が開発した新しい計算アルゴリズムである R 行列法に、さらなる高速化を可能とする等価モデルを追加し、原子論に基づきながら、通常のパーソナルコンピュータを用いても短時間処理が可能となっています。このシミュレータを用いることにより、原子配置乱れのあるナノワイヤトランジスタの特性などを計算することができます(図 5)。

図 5:原子配置乱れのあるナノワイヤトランジスタのデバイスシミュレーション。シリコンナノワイヤの分子動力学法熱酸化シミュレーション(早稲田大学・渡邉孝信教授より提供を受けた)を実行し、現実的な原子配置を有するナノワイヤトランジスタモデルを構築し、非平衡グリーン関数法に基づく量子輸送シミュレーションにより、電子状態および輸送特性を計算した。一番下の図は、キャリア密度分布を表しており、n型の場合は、キャリアは中心軸(z=0)付近を流れているが、p型の場合は、断面方向に広がって流れている様子が分かる。

連続体デバイスシミュレーションでは、ウィグナー・モンテカルロ法を用いて、量子効果と散乱、および原子論的バンド構造を取り入れた電子輸送シミュレーションが可能です。開発したシミュレータを用いて、ソース・ドレイン間直接トンネリングを考慮した化合物半導体 MOS型トランジスタの短チャネル化限界予測など、今後のデバイス開発指針の提言を行いました。また、コンパクトモデルに必要なパラメータを余分な仮定なしに抽出する手法を開発し、コンパクトモデルとのシームレスな接続を達成しました。

フォノン輸送シミュレーションでは、電子とフォノンの輸送方程式を連立させ、電子輸送とフォノン輸送とを統一的に扱うことができます。フォノン・モンテカルロ法を用いており、新規アルゴリズムを採用することにより、フォノン準弾道輸送効果が実際の極微細トランジスタ構造内でどのように顕在化するのかを初めて示しました。さらに、フォノン輸送シミュレーションに必要となる、極微細構造におけるフォノン状態を原子論的に計算するプログラムも開発しました。

コンパクトモデル開発では、ナノスケール MOS 型トランジスタでの弾道・準弾道輸送による電流電圧特性を表す簡易な解析式モデルを構築しました。デバイ

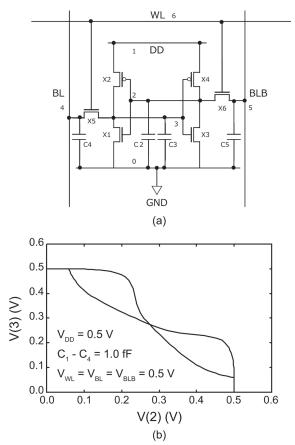

図 6: (a) ナノワイヤトランジスタで構成された SRAM 回路と、(b) 読み取り時のバタフライ曲線。NMOS は、チャネル長 10 nm、3 nm × 3 nm 正方形断面、PMOS は、2 nm × 4 nm 長方形断面(100)シリコンナノワイヤトランジスタ。

スの電流電圧特性を明示的かつ解析的な数式により表現し、その数式中で用いるパラメータを原子論的バンド計算および量子論的輸送計算と関連付けています。得られた NMOS および PMOS モデルをハードウェア記述言語 Verilog-A で記述し、回路シミュレータHSPICE に読み込むことにより、SRAM やリングオシレータなどの種々のナノワイヤ CMOS 回路のシミュレーションを行えます(図 6)。

開発した量子輸送シミュレータが、実際に多くのユーザーによって次世代ナノデバイスの性能予測に活用されるように、量子輸送シミュレータと汎用TCADシステムHyENEXSSとの接続を行いました。入力ファイルを共通化し、量子輸送シミュレーションの結果を、HyENEXSSの標準表示ソフトウェアで表示可能としています。

#### おわりに

本稿では、おもに、微細 MOS 型トランジスタの研 究について紹介しました。良く知られていますように、 パワーデバイスの分野でも、炭化ケイ素、窒化ガリウ ム、ダイヤモンドなどの新しい材料の導入が検討され ており、計算機を利用した材料選択指針への提言や、 デバイス・システムの最適化などが重要な研究課題と なっています。本研究室では、現在、そのような研究 にも積極的に取り組んでいます。他にも、シミュレー ション技術を活用した半導体デバイスの設計、信頼性 予測に関する研究や、フォノン輸送、熱電変換デバイ ス、熱管理技術に関する研究、集積回路システムレベ ルにおいては、低電圧動作アナログ・ディジタル集積 回路技術の開発や、非接触電力伝送技術を応用した小 型集積システムの実現に関する研究などを行なってい ます。今後とも、大阪大学工業会会員の皆様のご指導、 ご支援を賜りますようお願い申し上げます。

(電子 昭和61年卒 63年修士 平成3年博士)